[권신혁의 혁신포커스] “‘하이브리드 본딩’이 대세, 파티클 관리 관건”

기사입력 2024.02.26 16:32

.jpg)

▲한국실장산업협회(KPIA) 전기·전자·정보 산업별 기술 시장 및 표준 동향 세미나

좌성훈 교수, “첨단 패키징, 하이브리드 본딩으로 전환”

파티클 인한 보이드 이슈 해결 必, 플라즈마 다이싱 대두

파티클 인한 보이드 이슈 해결 必, 플라즈마 다이싱 대두

“패키징 기술이 후공정에서 전공정으로 옮겨가고 있다. 패러다임이 바꼈다. 이에 반도체 장비·소재기업들이 모두 다 하나같이 반도체 패키징 솔루션을 준비하고 있다.”

한국실장산업협회(KPIA)가 주관한 전기·전자·정보 산업별 기술 시장 및 표준 동향 세미나가 지난 21일 수원컨벤션에서 개최했다.

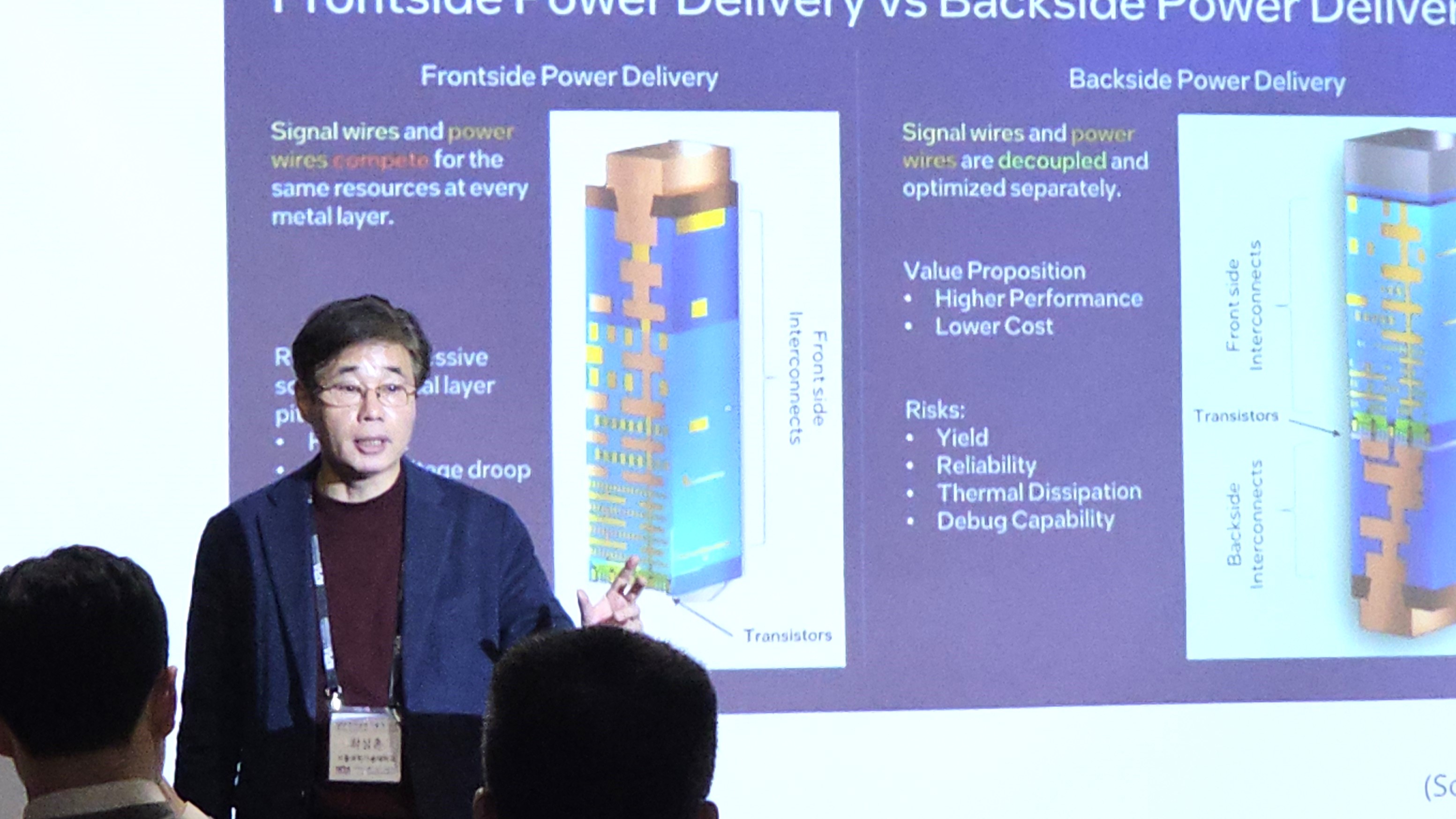

이날 좌성훈 서울과학기술대학교 교수는 ‘최신 반도체 패키징 기술 시장 및 국제표준동향’ 발표를 맡아 반도체 기술 격동기를 맡아 첨단 패키징 시대가 개막하고 있음을 피력했다.

현재 반도체 미세화 공정은 옹스트롬 단위에 접근하는 1나노대를 바라보고 있지만 양자 터널링, 디펙(Defect) 문제, 성능 대비 과도한 생산 단가 등 다양한 문제로 인해 무어의 법칙 달성에 어려움을 겪고 있다.

이에 반도체 첨단 패키징을 통한 출구전략이 유효하게 작용하면서 반도체 산업이 미세화 공정혁신에서 패키징 공정 혁신으로 그 중요성이 옮겨가고 있는 상황이다.

이러한 가운데 좌성훈 교수는 “요즘 웬만한 시스템반도체는 칩렛으로 만들고 있다”며 칩렛은 지난해까지 첨단 패키징에서 가장 주목도가 높았음을 강조했다. 이어 “오늘날에는 하이브리드 본딩이 많이 거론되고 있다”고 언급했다.

▲좌성훈 서울과학기술대학교 교수가 발표하고 있는 모습

하이브리드 본딩은 금속과 유전체, 두 이종 소재를 접합하는 기술로 구리는 구리와 접착하며 실리콘 산화막(SiO2)은 산화막끼리 접착하게 된다.

이러한 하이브리드 본딩은 기존 I/O 피치가 작아지며 발생하는 솔더의 강성 저하 문제를 고려하지 않아도 된다. 솔더는 접착 역할만 하고 구리 마이크로 필러를 이용해 열압착을 가해 견고한 접합을 가능케 한다.

이에 좌 교수는 “솔더링의 복잡한 과정이 생략됨으로써 하이브리드 본딩은 프로세스가 굉장히 간단해진다”면서 “따라서 연결 거리가 솔더링에 비해 짧아짐에 따라 파워 딜리버리도 좋아진다”고 설명했다.

가장 큰 문제는 디펙(Defect)이다. 공정 과정에서 발생하는 작은 파편, 불순물, 입자 등 파티클은 발생할 수밖에 없으며 하이브리드 본딩에서 파티클은 더 치명적인 문제를 야기한다.

좌 교수는 솔더 접합은 폴리머가 채워지며 파티클이 크게 문제 되지 않는 반면 하이브리드 본딩은 구리 접합이라 단단한 물질이기에 파티클이 있다면 접합이 되지 않고 빈 공간(Void Area)이 발생하게 돼 버린다고 설명했다.

이에 하이브리드 본딩으로 향하는 첨단 패키징에서는 파티클을 관리할 수 있는 기술력이 핵심이며, 최근 다이싱에선 파티클 문제를 최소화하기 위한 방향성에서 플라즈마 다이싱이 대두되고 있는 것으로 전해졌다.

좌성훈 교수는 “현재 칩렛 및 하이브리드 본딩은 기술 발전이 너무나 빠르게 진전되고 있기에 관련 국제 표준은 전무한 상태”라며 “반도체 기업들이 하이브리드 본딩에 맞는 공정으로 옮겨가고 있는 추세에 주목해야 한다”고 덧붙였다.

많이 본 뉴스

[열린보도원칙] 당 매체는 독자와 취재원 등 뉴스이용자의 권리 보장을 위해 반론이나 정정보도, 추후보도를 요청할 수 있는 창구를 열어두고 있음을 알려드립니다.

고충처리인 장은성 070-4699-5321 , news@e4ds.com